# Implementation of Adaptive Equalizer using FPGA

### Rupanjali Grover<sup>1</sup>, Baljit Kaur<sup>2</sup>

<sup>1</sup>SSIET ,Derabassi Chandigarh, 140507 *Er\_rupanjali@yahoo.com*

<sup>2</sup>Associate Professor, SSIET Chandigarh, 140507

Abstract: The quality of transmitted channel is deteriorated by channel imperfections. This results in high bit error rate at the receiver which in turn makes recovering the original signal difficult. Channel response is dynamic in nature and therefore to decrease bit error rate, adaptive equalizer is generally used at receiver end. The purpose of this paper is to present the FPGA implementation of adaptive equalizer.

Keywords: Channel imperfection, Adaptive equalizer, bit error rate

### 1. Introduction

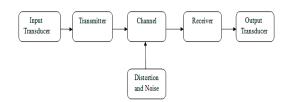

Signal is transmitted from one point to another via communication channel. This acts as a medium for signal to propagate from transmitter to receiver. Decoder is used at the receiver end decoder to recover the original signal.

Fig.1The basic communication model

The channel have different characteristics like channel, phase distortion, signal attenuation, bandwidth etc. These characteristics degrades the transmitted signals at some measure. The aim of the receiver is to recover the original symbols without error, the distortions or inter-symbol, interference (ISI) caused by the channel, noise and other sources are tried to be minimized. Channel imperfections like amplitude and phase dispersion are removed by equalizers which results in the interference of the transmitted signals with one another. In most of the digital communications applications, the channel transfer function is not known at enough level to incorporate filters to remove the channel effect at the transmitters and receivers. Generally channel response is time varying and an equalizer must be designed which could track these changes. An adaptive equalizer could do this. Various adaptation algorithms have been proposed in literature, but due to its simplicity and less implementation complexity, least mean square (LMS) algorithm has been used for the proposed design.

### **II. BASICS OF EQUALIZATION PROCESS**

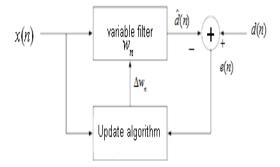

Equalizer generates the inverse characteristics of the channel and combination of channel and equalizer results in a flat frequency response and linear phase. To compensate for the distortions, the adaptive equalizer use training and decision directed modes [11]. The general structure of the adaptive filter as [2] shown in Fig.2.

#### Fig.2 Adaptive filter

The input signal is the sum of a desired signal d(n) and interfering noise v (n)

$$x(n) = d(n) + v(n) \tag{1}$$

The variable filter has a Finite Impulse Response (FIR) structure. For such structures the impulse response is equal to the filter coefficients. The coefficients for a filter of order p are defined as

$$w_n = [w_n(0), w_n(1), ..., w_n(p)]^T$$

(2)

the error signal or cost function is the difference between the desired and the estimated signal

$$e(n) = d(n) - d(n) \tag{3}$$

$\wedge$

The variable filter estimates the desired signal by convolving the input signal with the impulse response. In vector notation this is expressed

$$\hat{d}(n) = w_n * x(n) \tag{4}$$

Where

$$x(n) = [x(n), x(n-1), ..., x(n-p)]^{T}$$

(5)

is an input signal vector. Moreover, the variable filter updates the filter coefficients at every time instant

$$w_{n+1} = w_n + \Delta w_n \tag{6}$$

Where  $\Delta w_n$  is a correction factor for the filter coefficients. The adaptive algorithm generates this correction factor based on the input and error signals. This paper presents the comparison of some of the channel equalization techniques. The paper also presents FPGA implementation of Fractionally Spaced Equalizer.

# III. FPGA IMPLEMENTATION OF ADAPTIVE EQUALIZER

For implementing the proposed fractionally spaced equalizer, Xilinx 9.2i software has been used. VHDL code has been generated using system generator tool and resource and power utilization have been calculated using ISE software.

| Table 1: Resource Utilization for the Targeted FPGA |      |           |             |  |  |

|-----------------------------------------------------|------|-----------|-------------|--|--|

| Logic                                               | Used | Available | Utilization |  |  |

| Logic<br>Utilization                  | Used  | Available | Utilization |

|---------------------------------------|-------|-----------|-------------|

| Number of<br>Slice Flip<br>Flops      | 2,222 | 67,584    | 3%          |

| Number of 4<br>input LUTs             | 1,060 | 67,584    | 1%          |

| Logic<br>Distribution                 |       |           |             |

| Number of<br>occupied<br>Slices       | 1,645 | 33,792    | 5%          |

| Total<br>Number of<br>4 input<br>LUTs | 1,981 | 67,584    | 2%          |

Table 1 shows the resource utilization. Results show that the proposed design has very less resource utilization.

### **IV.CONCLUSION**

Adaptive equalizers are used to generate the reverse characteristics of the channel and has the adaptation property, i.e. capability to track the changer in channel characteristics. In this paper a fractionally spaced equalizer has been implemented on an FPGA. Fractionally spaced equalizes have better equalization capability as compared to conventional equalizers. Xilinx 9.2i software has been used to synthesize the design and VHDL code has been generated using System Generator tool.

### REFERENCES

Г

[1] Adinoyi, S. Al-Semari and A. Zerquine (Jan. 1999) Decisionfeedback equalisation of coded I-

Q QPSK in mobileradio environments. Electron. Lett., 35:13-14, No.1.

- [2] Antoinette Beasley and Arlene Cole-Rhodes (2005) Performance of Adaptive Equalizer for QAM signals. IEEE,Military Communications Conference, 4: 2373 - 2377.

- [3] B. Petersen, D. Falconer (1994) Suppression of adjacent-channel, cochannel and intersymbol interference by equalizers and linear combiners. IEEE Trans on Communication, 42: 3109-3118.

- [4] B.P.Lathi (1998) Modern Digital and Analog Communications system. Third edition. USA: Oxford University Press.

- [5] D. N. Godard (Nov. 1980) Self-recovering equalization and Carrier Tracking in Twodimensional Data communications Systems. IEEE Trans. Communication, COM-28(11):1867-1875.

- [6] J.R. Treichler, I. Fijalkow, and C.R. Johnson, JR. (1996) Fractionally Spaced Equalizers. IEEE Signal Processing Magazine, 13(3):65-81.

- [7] Kevin Banovic, Mohammed A.S., Khalid Esam Abdel-Raheem (2007)FPGA and Implementation of a Configurable Complex Blind Equalizer. International Adaptive IEEE Symposium on Signal Processing and Information Technology, 150-153.

- [8] R.D. Gitlin and S. B.Weinstein (February 1981) Fractionally-Spaced Equalization an improved digital transversal Equalizer. Bell Syst. Tech. J., 60 (2):275-296.

- [9] S. U. H. Qureshi (1985) Adaptive equalization. Proceedings of the IEEE, 73(9):1349-1387.

- [10] Vladimir D. Orlic and MiroslavLutovac (2009) A solution for efficient reduction of intersymbol interference in digital microwave radio. TELSIKS, 15(2):463-464.

- [11] Wang Junfeng and Zhang Bo (2010) Design of Adaptive Equalizer Based on Variable Step LMS Algorithm. Proceedings of the Third International Symposium on Computer Science and Computational Technology (ISCSCT '10) Jiaozuo, P. R. China, 256-258.

- [12] Zhou Jiang, Zhi Liu, Rong-Hua Jin and Xiao-Yang Zen (2006) Design of Dual-mode Equalizer for QAM Demodulator in FPGA,8th International Conference on <u>Solid-State and Integrated Circuit</u> <u>Technology.</u>

## **Author Profile**

### RUPANJALI

Rupanjali Grover is an M.Techstudent , in the final year of the course.

BaljitKauris an AP in a reputed college of PTU.